导语

本章的主要内容是介绍PCB设计的前期处理:原理图生成的前期准备工作,原理图如何生成网表的方法;那么,Allegro的常见网表导入方式有哪两种呢?

1原理图网表生成前的准备工作

1.1 Part的Pin的定义:

为了能顺利产生网络表,必须对Part Pin的Name、Number和Type做好定义,并且同一Part的Name和Number是不能重复的,只有当Pin Type为Power时Pin Name才允许相同。

1.2 Part的PCB Footprint的定义:

在Edit-Properties中设定PCB Footprint

当然先需要做好器件PCB封装库,并把它们放在。/symbols下,建议设计者建立自己的库目录

1.3 不同Part的Device值设定必须不同

在Device栏设定值,不同Part的值不能相同,或者统一不做命名;生成网表时原理图软件会自动命名,使用器件的封装等相关参数。

如:“CAP NP_0805_0.1U”这就是Device自动命名的结果。

1.4 NC Pin的定义

有时工程师在建立原理图零件的时候会把没有连接Net的Pin定义省略,而这些Pin在PCB Layout中必须存在,针对这种情况需要对原理图里的零件Part做一下设定:

在原理图软件中双击Part进入Edit Properties新增一项NC Property,Property的Name需大写NC,在Value输入零件的NC Pin

1.5 有些字符在导入网络表时是不允许的,例如: “!”

2原理图网表生成

方法一:

用Cadence自带的原理图OrCAD Capture打开原理图;

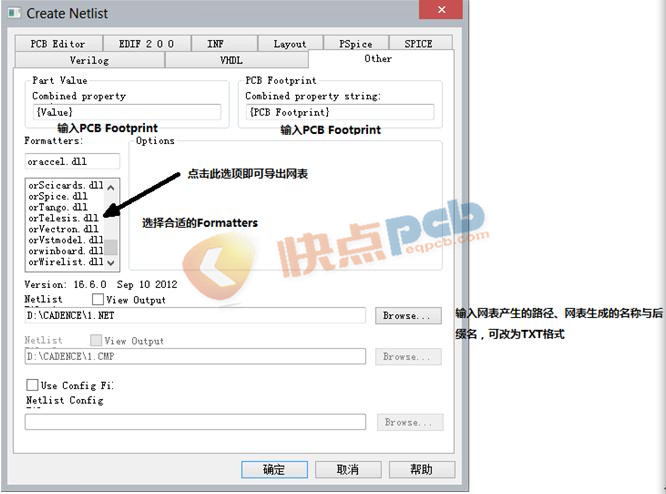

单击图 按钮 或执行菜单命令Tools/Create Netlist…,弹出对话框如下图:

按钮 或执行菜单命令Tools/Create Netlist…,弹出对话框如下图:

依如下步骤进行操作产生网表。

方法二:

用Cadence自带的原理图OrCAD Capture打开原理图;

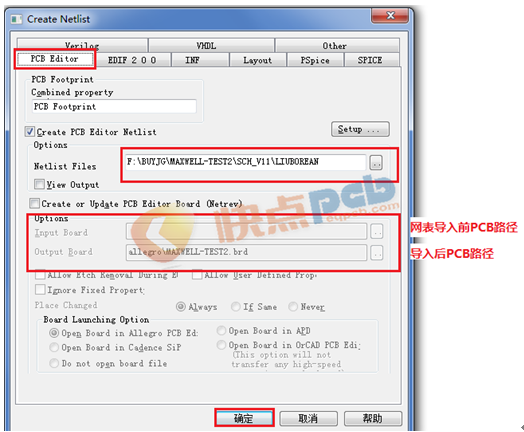

单击图 按钮 或执行菜单命令Tools/create Netlist…,弹出对话框如下图:

按钮 或执行菜单命令Tools/create Netlist…,弹出对话框如下图:

依如下进行操作,

确定成功就会打开一块新的PCB设计文件(。brd文件后缀)

大家学会了吗?

如果没有学会可以上我们快点PCB平台官网观看视频~